Cortex M4 Arm Developer

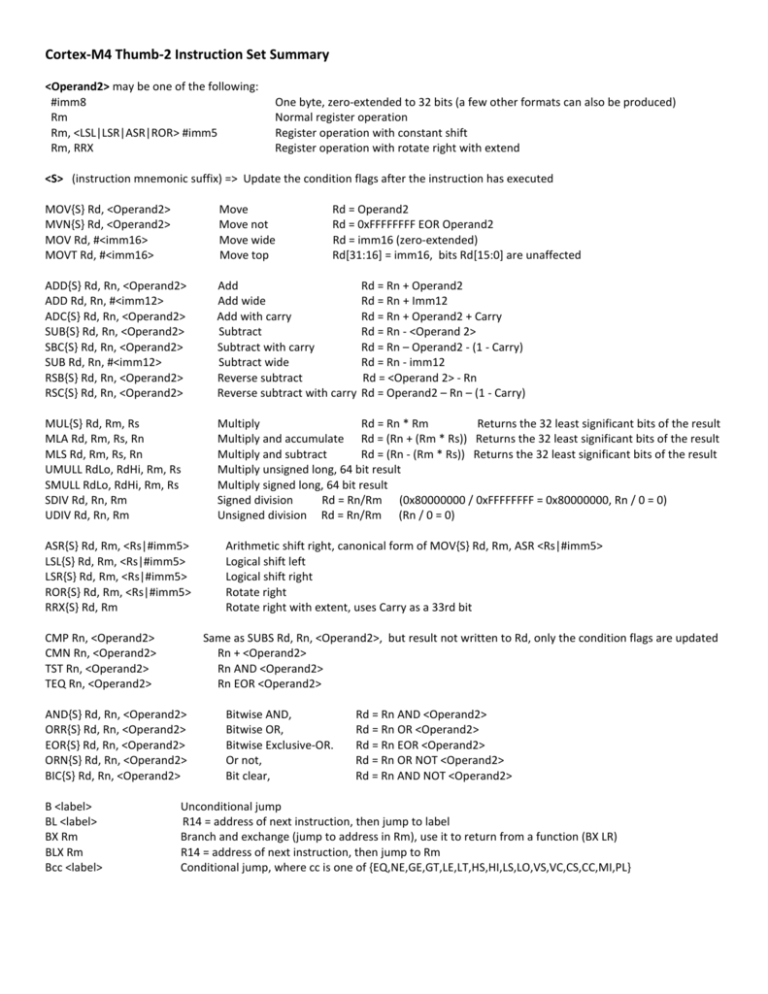

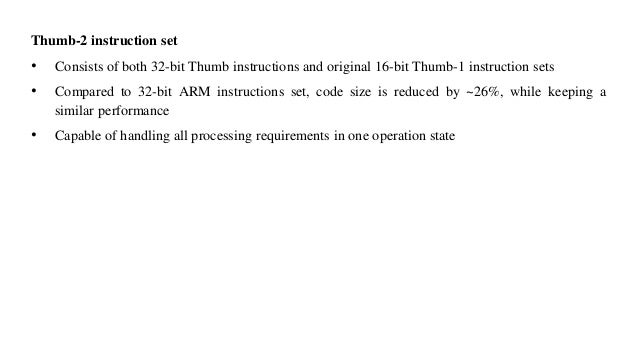

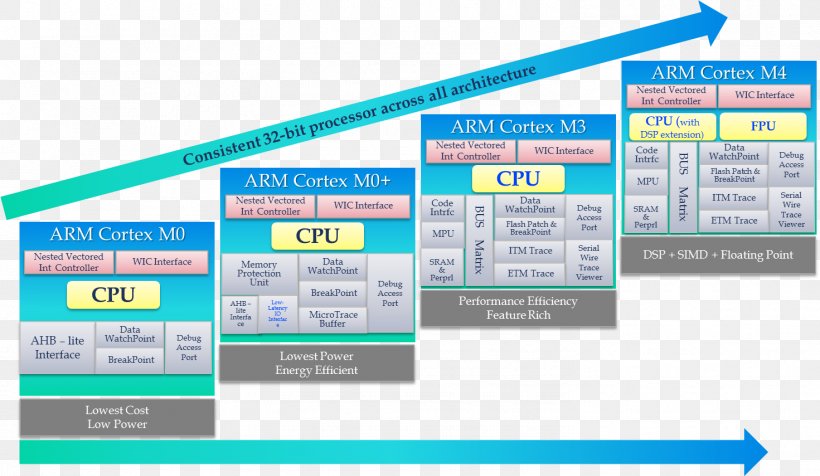

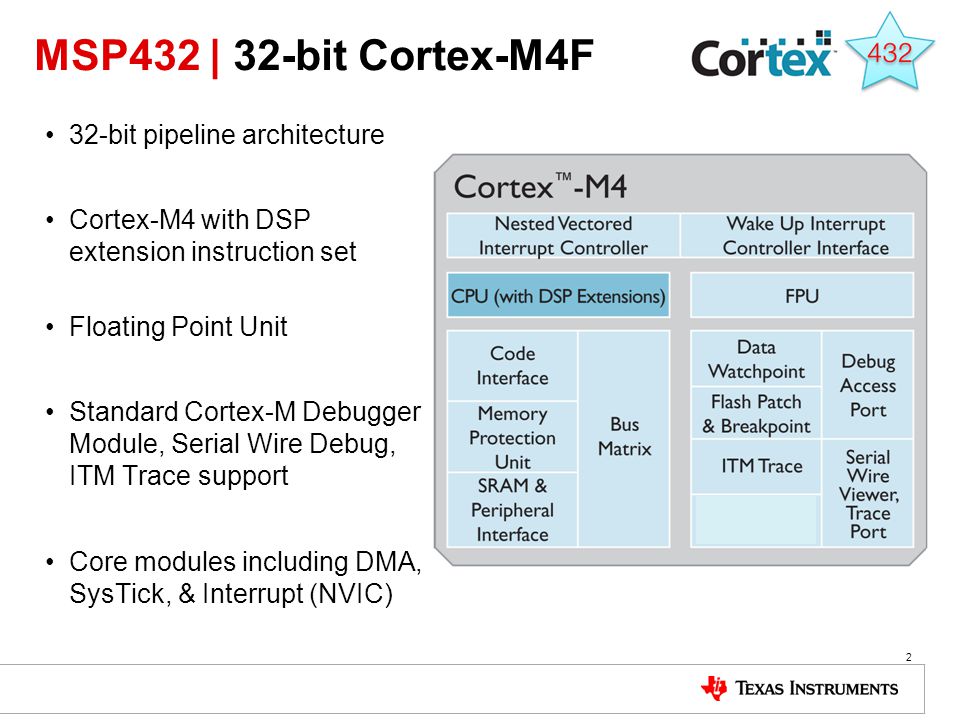

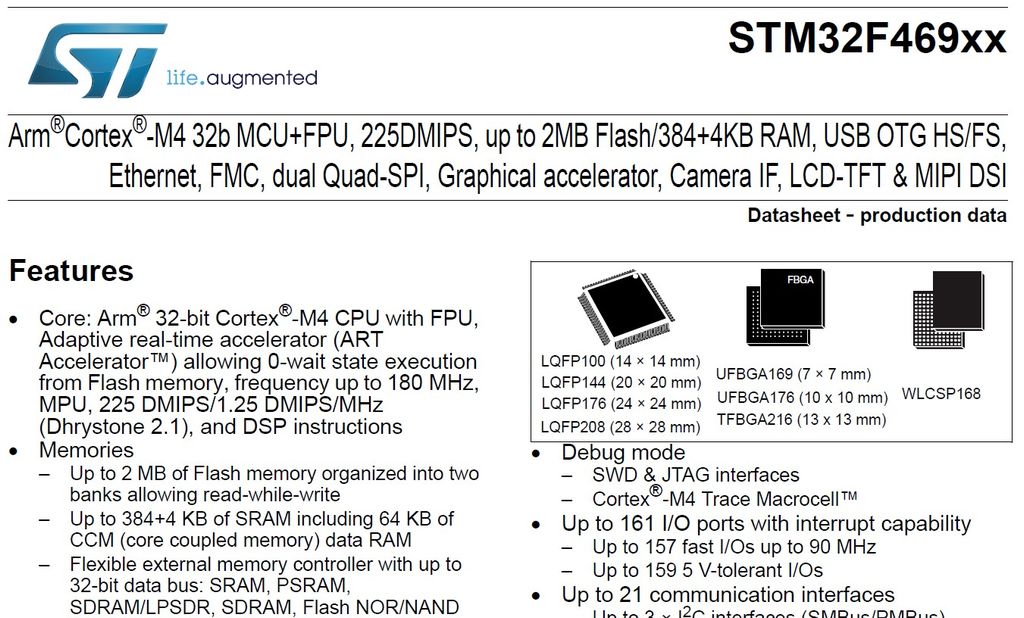

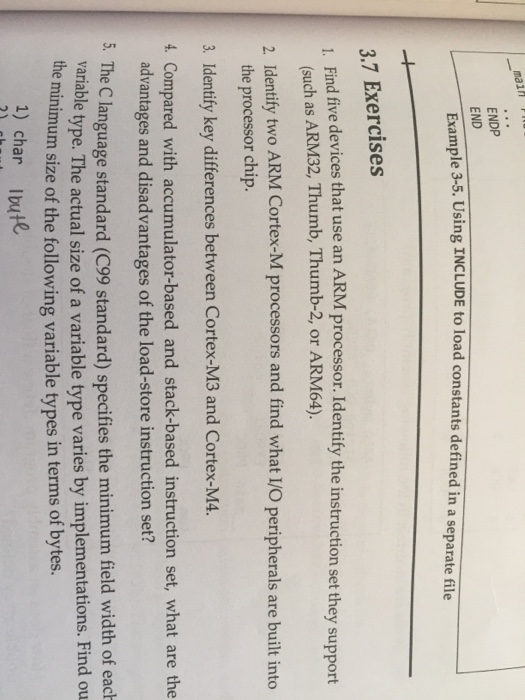

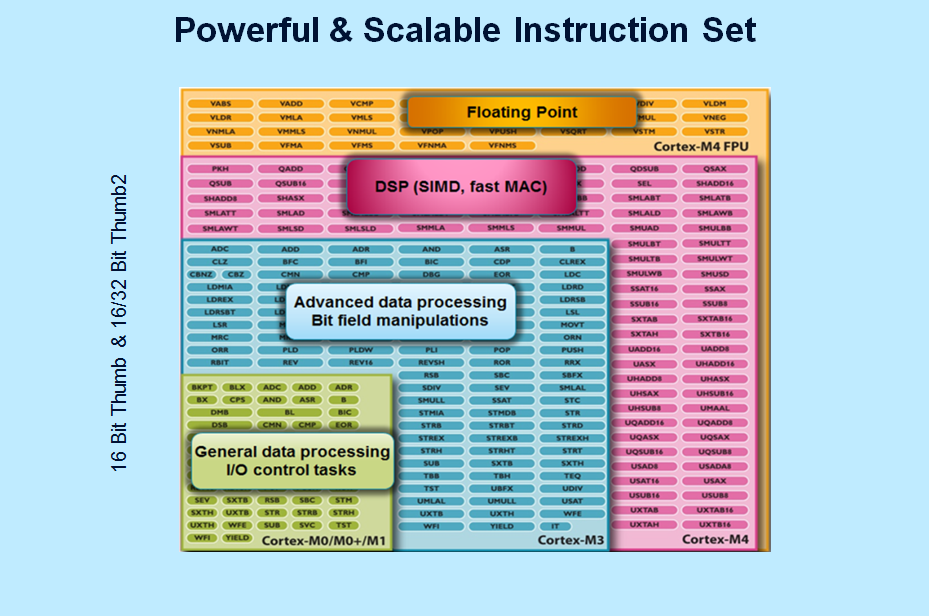

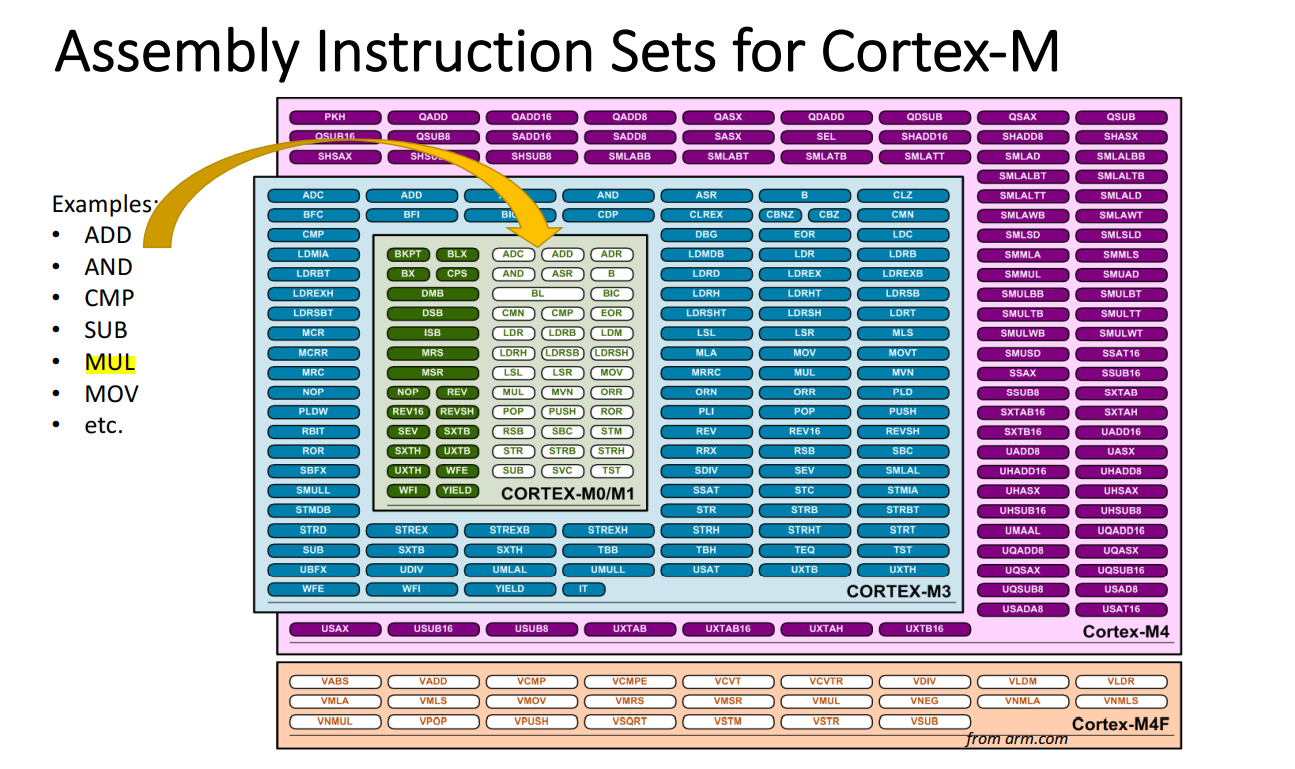

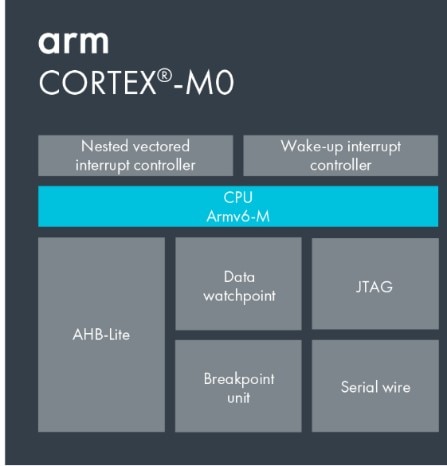

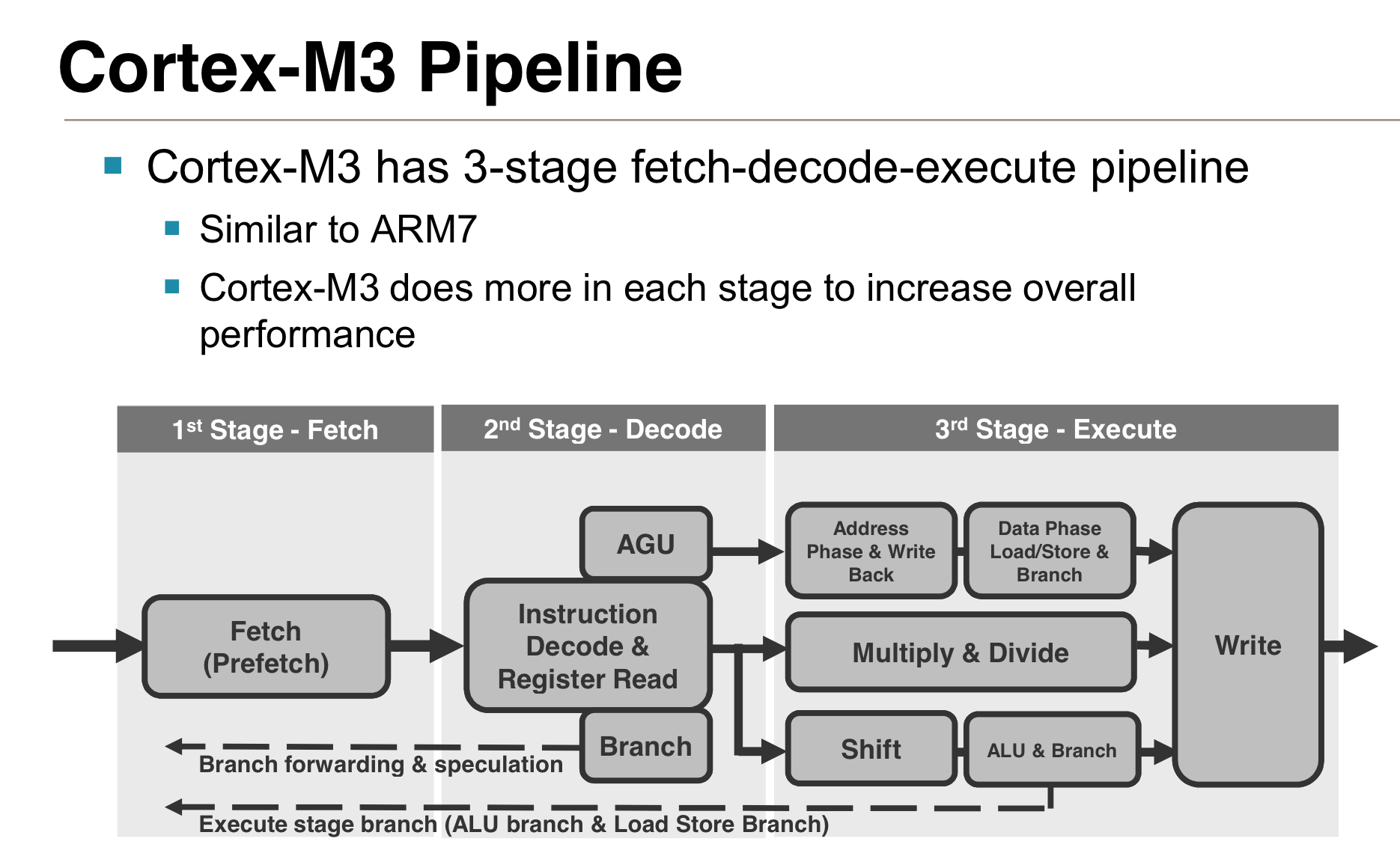

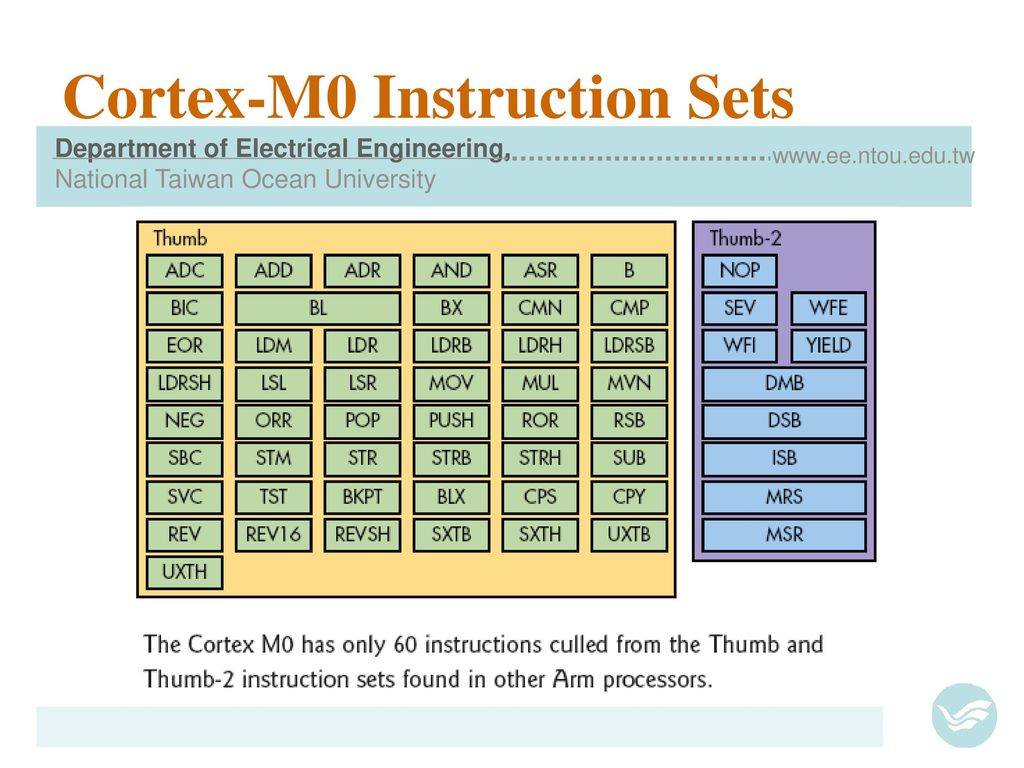

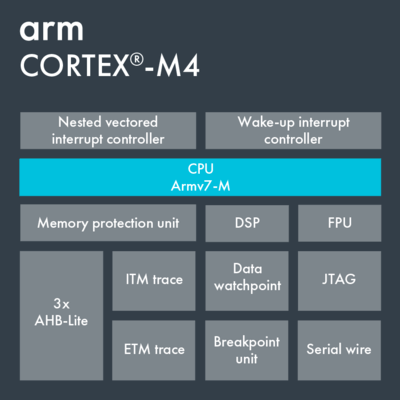

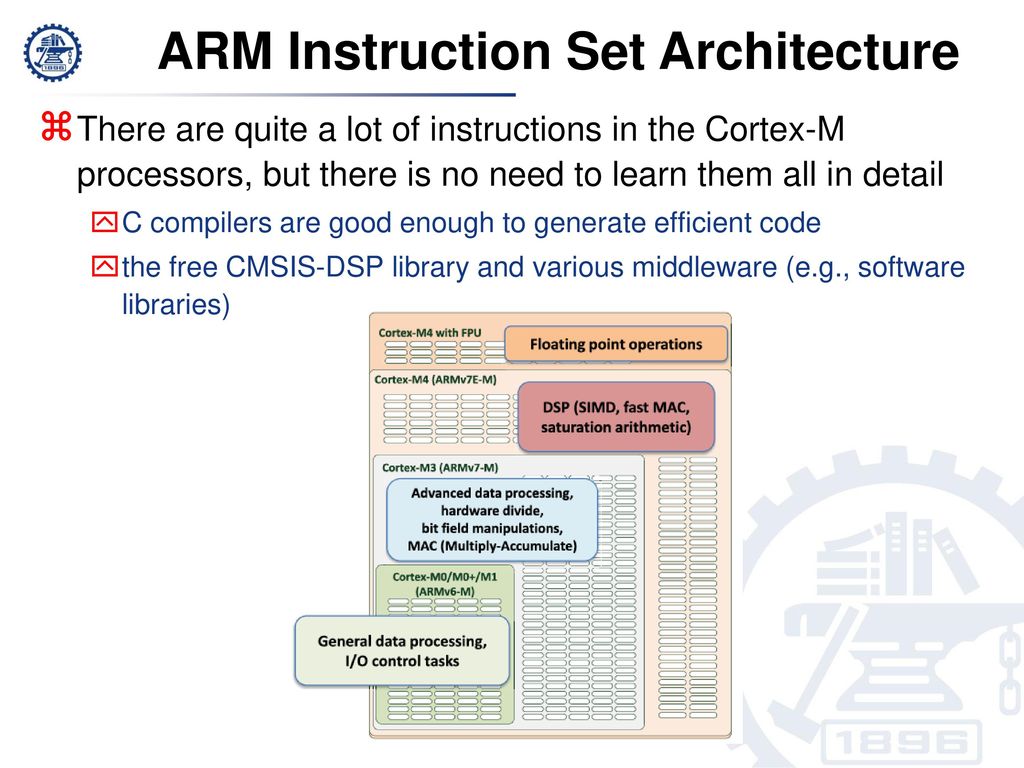

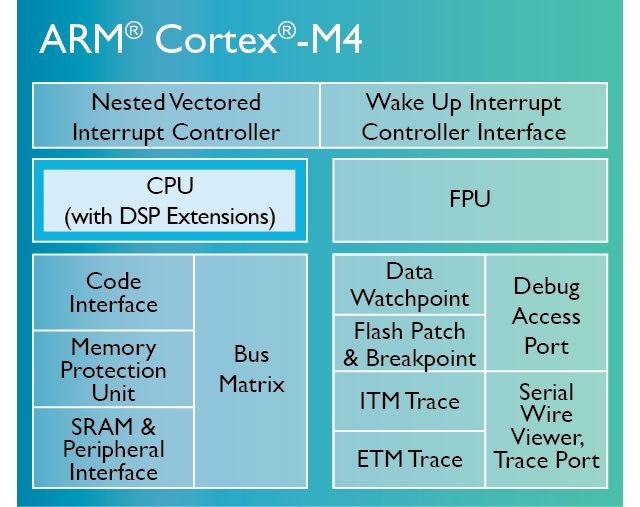

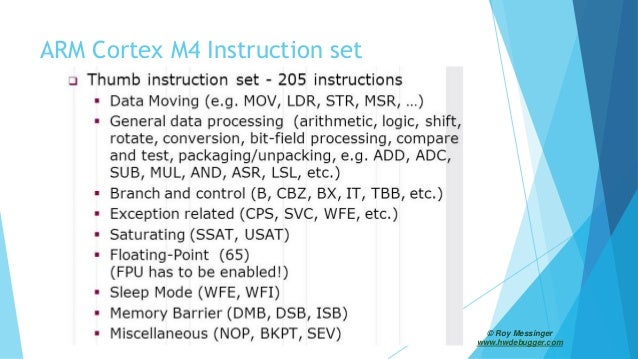

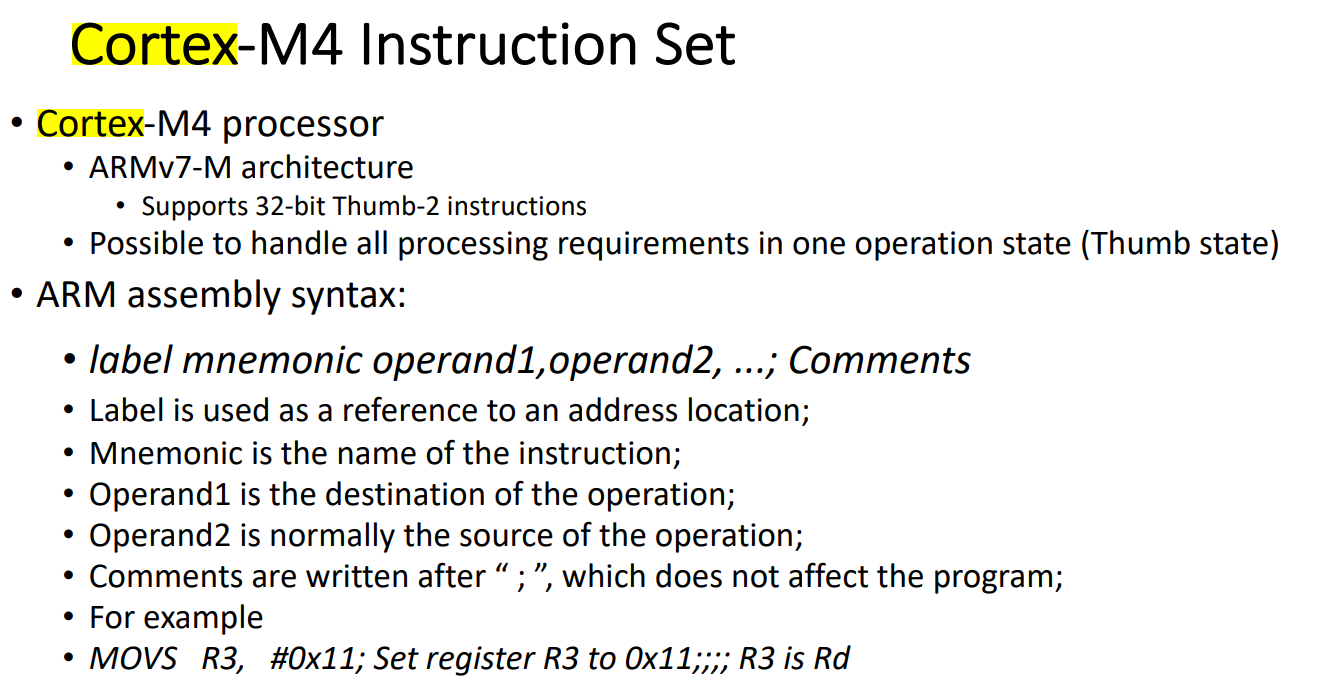

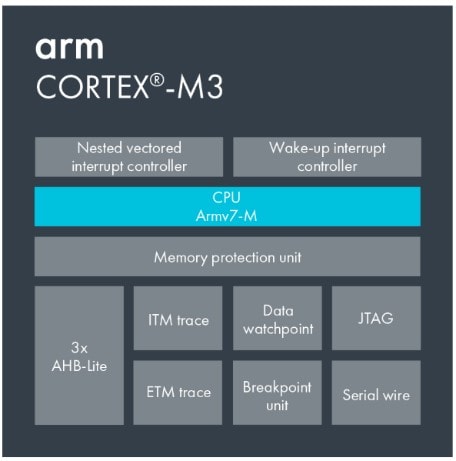

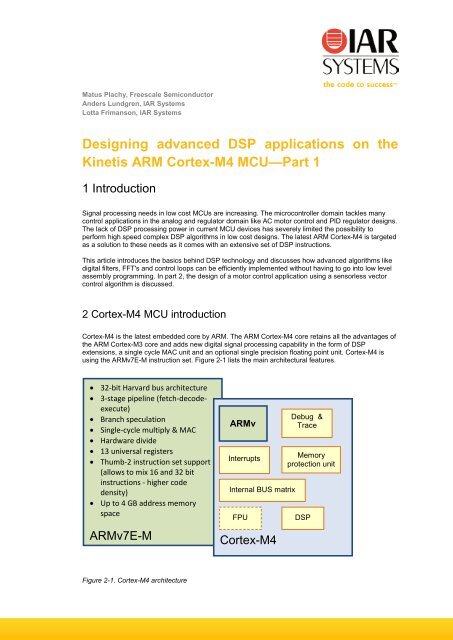

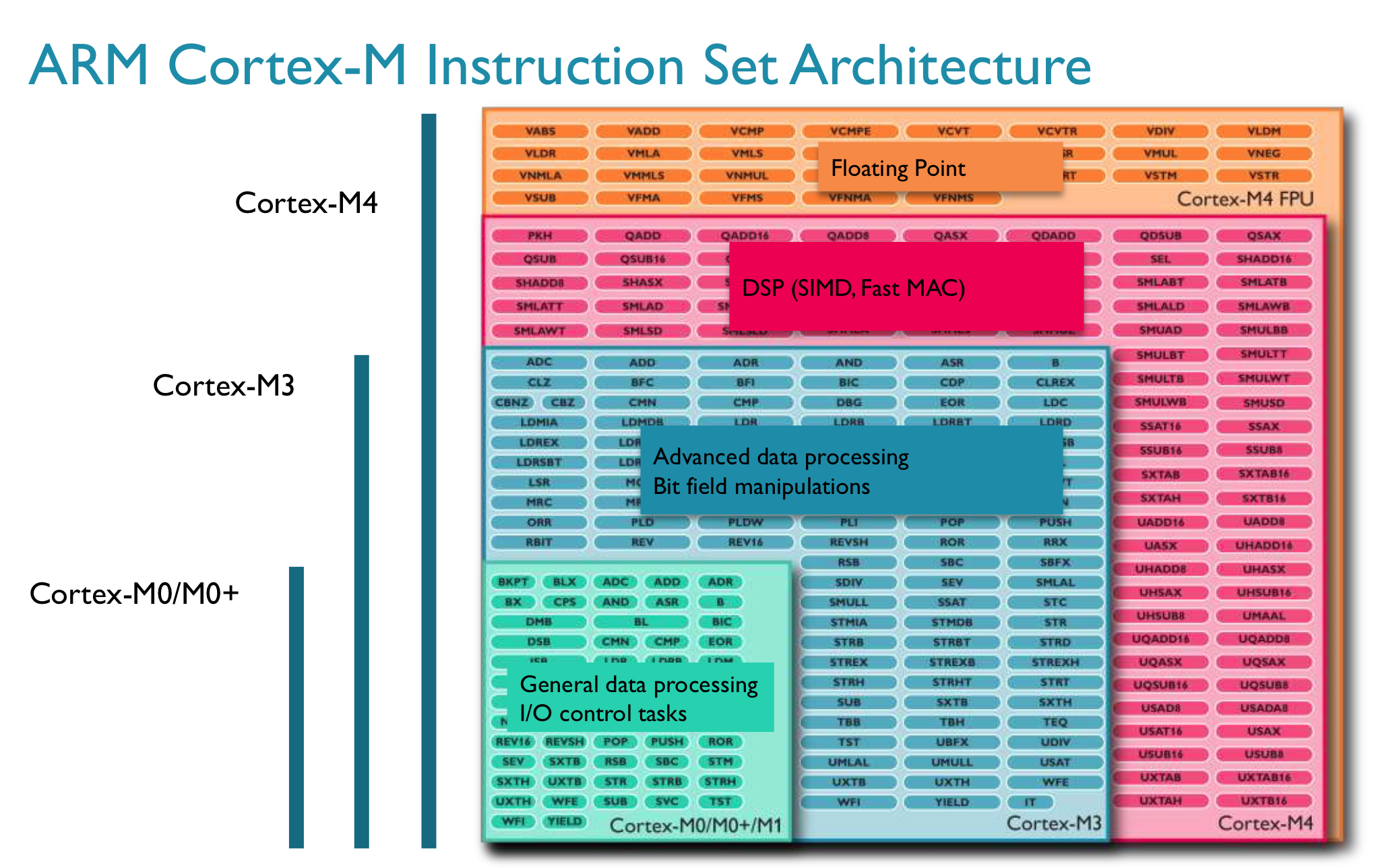

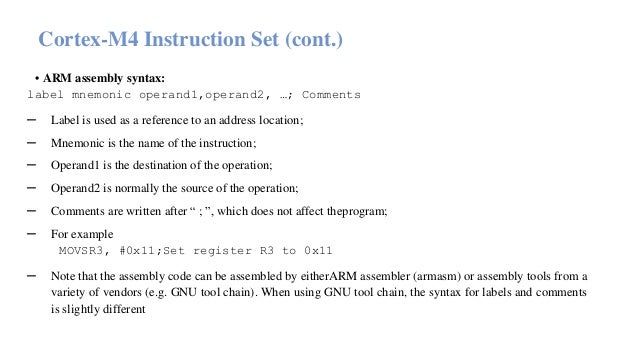

The target processor's "instruction set" is the set of capabilities that the core knows how to execute The LPC chips are grouped into related series that are based around the same 32bit ARM processor core, such as the CortexM4F, CortexM3, CortexM0, or CortexM0 Internally, each microcontroller consists of the processor core, staticCortexM4 Cortex M3 Total 60k* Gates ARMv7EM Architecture Thumb2 only DSP extensions Optional FPU (CortexM4F) Otherwise, same as CortexM3 Implements full Thumb2 instruction set Saturated math (eg QADD) Packing and unpacking (eg UXTB) Signed multiply (eg SMULTB) SIMD (eg ADD8)

Cortex m4f instruction set

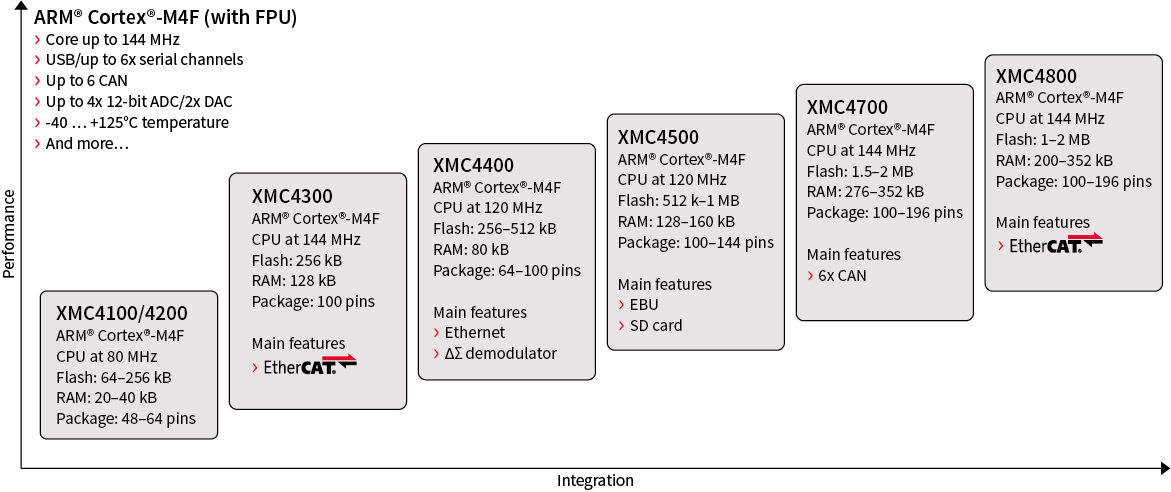

Cortex m4f instruction set-Cortex®M4F Based MCU TM4C123G LaunchPad™ Evaluation Kit The TM4C123G LaunchPad Evaluation Kit is a lowcost evaluation platform for Arm CortexM4F based microcontrollers Featuring a 80MHz Arm CortexM4F CPU, 256kB of flash, and 32kB of SRAM, the TM4C123GH6PM MCU provides integrated USB support for USB Host/Device/OTG andInstruction Set Simulator (ISS) for ARM CortexM4F An ISS is a software development tool that takes in instructions for a target processor and executes them The heart of an ISS is the model of the processor Imperas has developed a range of ISS products for use in embedded software development that utilize this fast Fast Processor Model

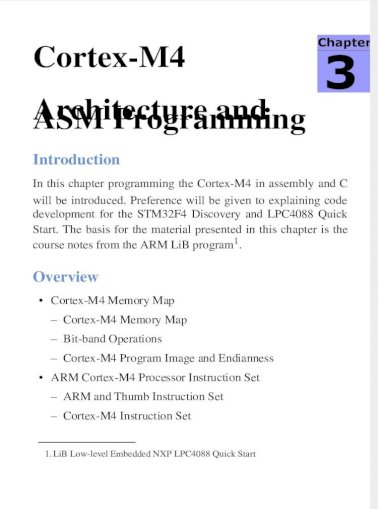

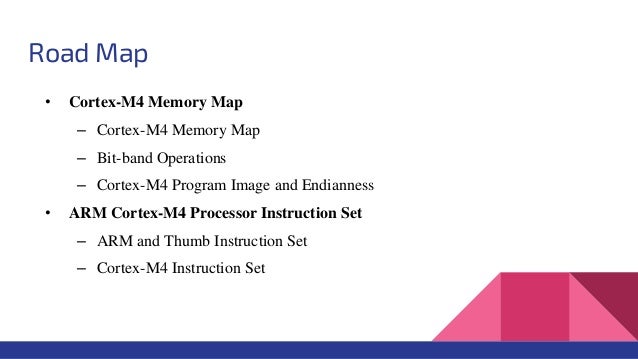

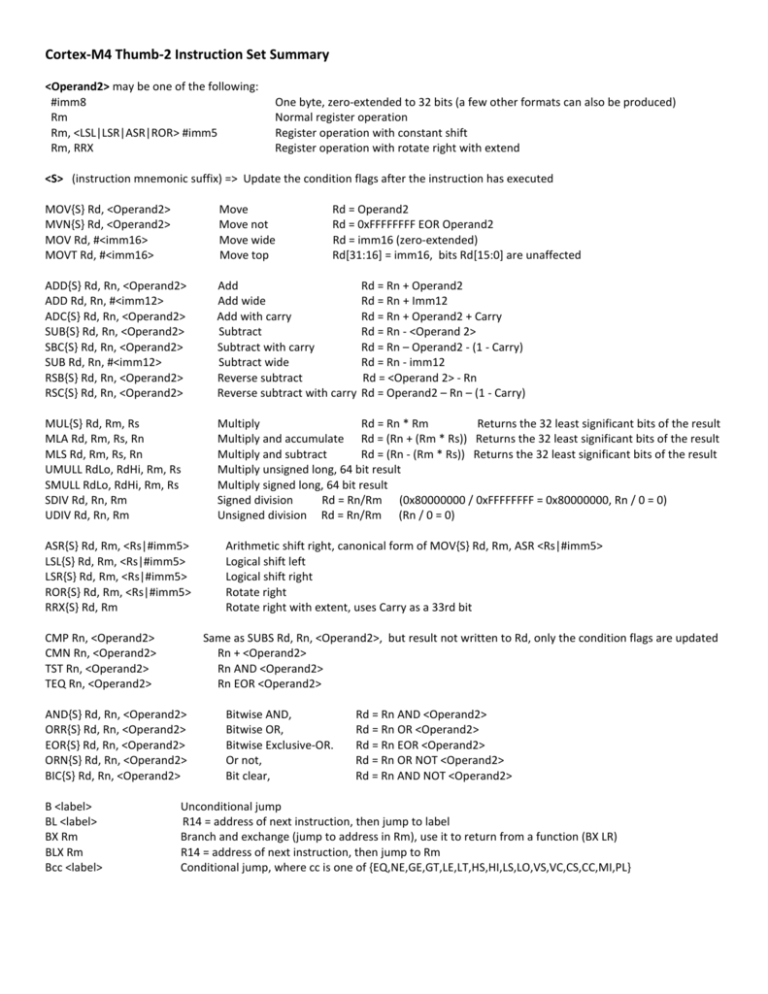

Cortex M4 Thumb 2 Instruction Set Summary

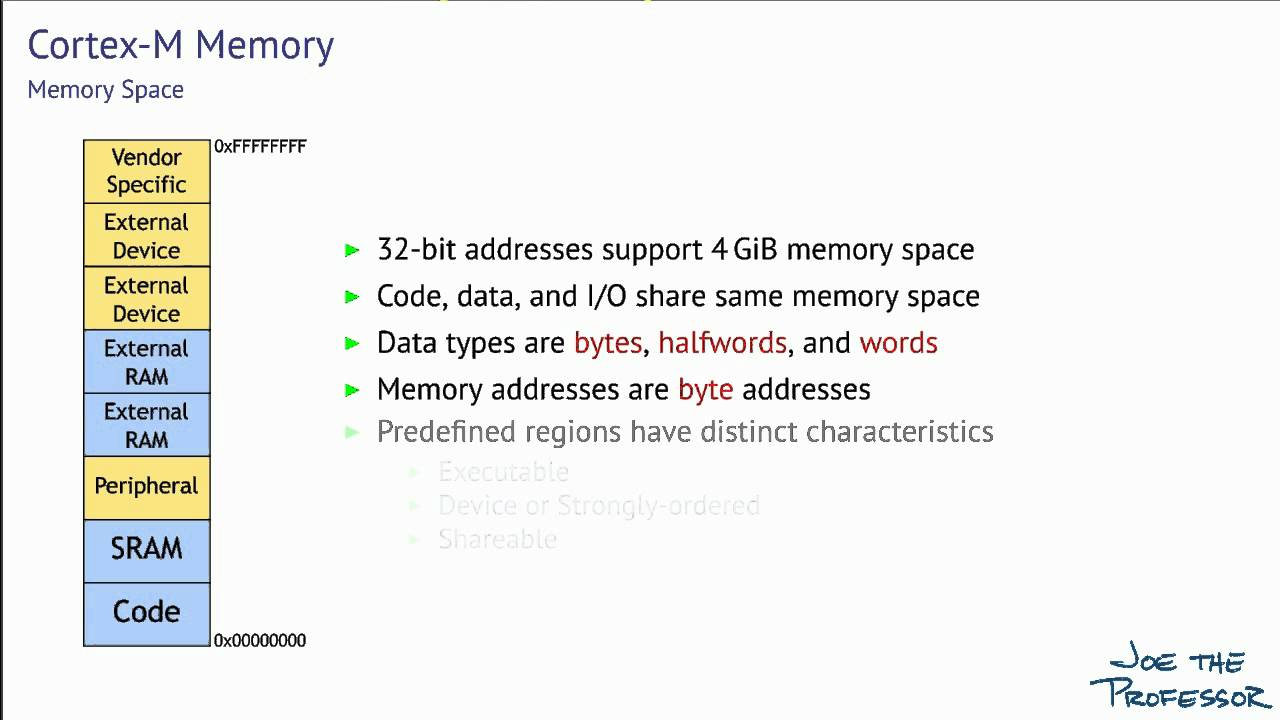

Cortex M3 M4F Instruction Set Technical User s Manual Rev A Arm Cortex M4 Manuals Embedded Systems Laboratory Using ARM Cortex M4 ARM Cortex M4 Architecture scribd com PM0214 Programming manual st com Atmel SMART SAM G55G SAM G55J Datasheet Cortex M4 Devices Generic User Guide Arm Developer ARM®Documentation – Arm Developer menu burger DOCUMENTATION MENU DEVELOPER DOCUMENTATION Back to search Important Information for the Arm website32bit Cortex®M4F CPU with FPU − 240 MHz maximum frequency, with a memory protection unit (MPU) − Singlecycle multiplication and hardware division − Floating point unit (FPU) − DSP instructions Memories − 256 to 1024 KBytes of Flash instruction/data memory − sLib configurable part of main Flash set as a libruary area with code excutable but secured, non

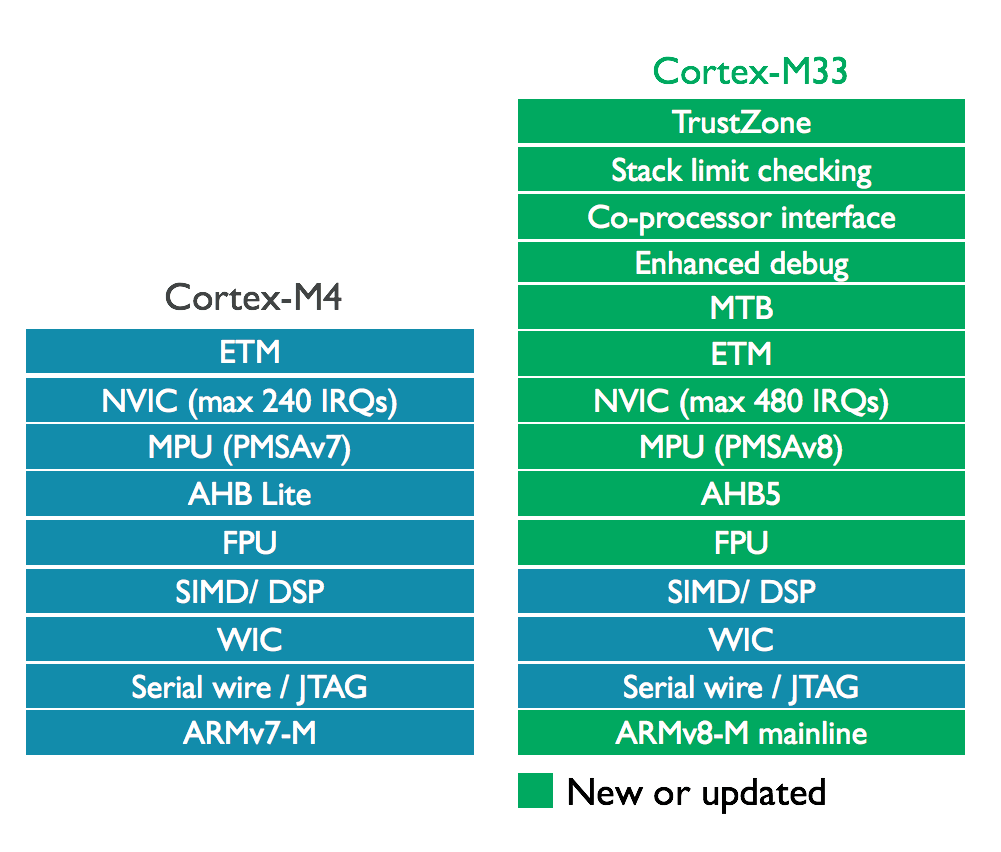

This guide contains documentation for the CortexM4 processor, the programmer s model, instruction set, registers, memory map, floating point, multimedia, trace and debug support Components include ETM, MPU, NVIC, FPB, DWT, ITM, AHB, TPIU, VFP CortexM4 Technical Reference Manual CortexM4 Technical Reference Manual ARM DDI 0439B Errata 01 VersionArchitecture Universität Dortmund Cortex M4 block diagram 2 Cortex M4 Embedded processor for DSP with FPU Universität Dortmund Cortex M4 vs M3 (b) The CortexM4 ISA is enhanced efficient DSP features including extended singlecycle cycle 16/32bit multiplyaccumulate (MAC), dual 16bit MAC instructions, optimized 8/16bitI've been looking for a list of the opcodes used in ARM Cortex M3/M4/M4F, without luck There are plenty of online references to the 32bit format of ARM instructions References to Thumb2 instructions are scarce, but available The version used in M variants, however, I cannot find!

Cortex m4f instruction setのギャラリー

各画像をクリックすると、ダウンロードまたは拡大表示できます

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |  Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Arm S Cortex M Even Smaller And Lower Power Cpu Cores | Arm S Cortex M Even Smaller And Lower Power Cpu Cores |

Model, instruction set and core peripherals The applicable products are listed in the table below The Cortex®M4 processor used in STM32F3 Series, STM32F4 Series, STM32G4 Series, STM32H745/755 and STM32H747/757 Lines, STM32L4 Series, STM32L4 Series, STM32WB Series, STM32WL Series and STM32MP1 Series, is a high performance 32bit processor• ARM CortexM4 Integration and Implementation Manual (ARM DII 0239) • ARM ETMM4 Technical Reference Manual (ARM DDI 0440) • ARM AMBA

Incoming Term: cortex m4f instruction set, cortex-m3/m4f instruction set,

0 件のコメント:

コメントを投稿